本文通过对现有用于微显示的LED芯片使用过程分析,指出目前使用过程中主要限制问题,设计三种电极焊盘表面结构,并完成芯片制作;通过对三组实验品的外观及固晶后推力进行对比评估,指出三组芯片焊盘表面电极结构各自的优缺点及适用性,对后续芯片选择具有一定指导意义。

前言

随着近年来的技术发展,作为LED在显示上的一个重要应用,小间距显示屏在进入室内显示后,逐渐走向成熟。传统的小间距显示由于像素间距的影响以及分立器件的固有缺陷,依然存在显示视距不足、摩尔纹等现象,为满足人们不断追求显示效果的需求,以及进一步扩展应用领域,小间距显示在往更小点间距发展的道路上不断前进,这就意味这芯片的尺寸不断减小,MiniLED由于其能够避免原有芯片的种种缺陷,而成为更小点间距的唯一选择,同时也成为近两年业界研究的热点。

今年以来各类相关应用也不断展出,目前常规MiniLED结构皆采用倒装结构,芯片尺寸在*um之间,受到芯片及电极NP电极间隔尺寸的限制,芯片的焊盘尺寸较小。同时为克服分立器件尺寸对点间距限制,MiniLED大多采用集成封装(COB)方式进行,其对作业过程中的稳定性一致性等要求较高,因此在封装过程中实现稳定可靠的芯片与基板的焊接是MiniLED应用过程最重要的环节之一。

本文从芯片端出发,制作不同电极焊盘结构,通过对比焊接过程后的参数表现,分析对芯片及封装的影响,为后续使用提供一定经验。

机理分析及实验设计

针对倒装LED芯片焊接,常规方式是回流焊及共晶焊两种方式。

其中常规回流焊方式,封装过程中通过锡膏固定方式进行,对应电极表面为Au结构,具体的需要在基板对应焊盘位置点锡膏,再固定芯片,然后再按照一定的温度曲线通过回流焊炉进行高温固化,锡膏的选择决定了固化所有需要的温度,通常会在~℃之间进行选择,温度相对较低,与芯片制程温度基本一致,对芯片结构影响较小,同时由于MiniLED芯片及焊盘尺寸较小,锡膏使用量及位置准确度极为重要,与此同时芯片电极焊盘对锡膏的适应性也较为重要,若防护不足,极易发生电极侵蚀而脱落情况。

另一种共晶焊,封装过程中通过助焊剂固定方式进行,对应芯片电极焊盘表面为AuSn结构,具体的需要在基板对应焊盘位置点助焊剂,再固定芯片,然后再按照一定的温度曲线进行高温固化,过程中由于AuSn材料本身共晶温度限制,通常最高温度在℃左右,对芯片结构及辅材等高温的稳定要求较高,但其避免了小尺度下锡膏控制的问题。

在以上两种方式之外,另一种目前在IC集成封装工艺中用到的镀锡工艺则集合了以上两种方式的优点,对应芯片电极焊盘表面采用Sn结构,具体的需要在基板对应焊盘位置点助焊剂,再固定芯片,然后按照一定的温度曲线进行高温固化,温度方面与常规回流焊类似,芯片电极焊盘表面SnAg成份决定了固化所使用的温度,目前常用温度在℃左右,该方式一方面避免了锡膏情况下的精准控制问题,另一方面固化温度也在相对较低位置,但芯片制程相对复杂,同时芯片结构对最终效果影响较大。

考虑以上三种方式对芯片及封装效果的影响,本文采用三种方式制作同尺寸MiniLED芯片,再按照对应焊接所需温度曲线进行芯片与基板焊接,然后从外观、性能、推力等方面进行测试分析。

实验准备及实施

1、芯片制备

按照现行芯片工艺,选择外延片进行常规工艺流水,电极焊盘制作前暂停分为3组,其中组1在电极焊盘制作时采用现行Au电极结构,焊盘厚度2.4um,组2在常规电极制作后,采用使用热蒸发方式,使用有研亿金新材料有限公司AuSn材料(99.%)制作AuSn焊接层(Au80%:Sn20%),厚度4um,组3在常规电极制作后,在电极焊盘位置制作焊锡层(Sn97%:Ag3%)焊层厚度10um,从制作过程看,常规Au电极及AuSn镀层采用蒸发方式进行,整体良率较为稳定,焊锡层制作时,由于过程中含有一定腐蚀性成份,需要在芯片表面非镀膜区域做钝化加强,防止作业过程中出现芯片结构的损伤,同时整个镀膜制作过程中参数调整对最终良率影响较大,三组样品焊盘表面SEM形貌正面及侧面对照如下:

其中图1为组1表面为Au结构芯片;图2为组2表面为AuSn结构芯片;图3为组3表面为镀Sn结构芯片;由上图可以看出,组1及组2样品在完成电极制作后,焊盘表面较为平整,但一次电极结构表现明显,组3由于制作方式原因,焊盘表面相对粗糙,但由于整体厚度较厚,底层一次电极形貌未表现出,同时由于Au材料属性限制,在测试过程中,测试探针极易在焊盘表面形成明显痕迹。

在完成芯片前道作业流水后,将3组按照常规方式进行研磨划裂,同机台测试结果如下:

表1测试汇总

由以上测试结果,3组芯片光电性能参数基本一致,综合良率基本一致,其中组3,Ir良率略低,通过观察芯片表面,部分区域出现金属沾污,这主要是由于制作镀锡层后,溶液清洗过程中产生,导致出现漏电通道产生漏电,这也是在该工艺实施过程中,最主要控制环节。

2、芯片封装

从以上3组制备完成样品中,各自选取50pcs参数相同晶粒进行封装样品制作,根据实验室条件,锡膏使用晨日科技ES0实验组2/3助焊剂使用晨日科技ES系列(粘附强度15mg/mm^2)固晶完成后使用型号为SIKAMAFalcon5C的5温区回流焊机进行,三组作业过程如下(回流焊曲线):

其中组1使用图a曲线,组2使用图b曲线

过温完成后,焊接形貌情况如下:

由图4显示:三组差异较为明显,其中组2、组3由于未使用锡膏,外观较好,完全避免锡膏过量的问题,组1封装在使用锡膏过程中,易发生类似锡膏过量导致的芯片歪斜现象,同时由于芯片焊盘间距为um,因此在锡膏过量情况下,固晶过程导致锡膏挤压流动,容易产生焊盘连同,形成漏电通道,造成最终失效。

结果与分析

使用型号为TRYMFM多功能推拉力测试机(下图a)对三组样品进行推力测试,数据采集效果曲线如图(下图b)。

每组实验品测试10pcs,对推力测试数据进行统计(表2),同时对推晶过程中掉落芯片电极表面进行SEM分析如下:

从推力测试汇总数据看,实验组3(镀Sn)推力明显高于组1及组2,组2推力最低,推落芯片焊盘完整,但形貌相对有一定差异。结合前述样品制作与封装过程推测:组1推力相对偏低与所使用锡膏粒径偏大有关,用于测试晶粒焊盘面积为76*62um,因此在封装过程中,会导致部分晶粒焊盘下锡量不足,进而表现为推力不足,在组1SEM图像上可以明显发现,有较大区域空洞位置,同样对于组2样品,受制于芯片结构设计原因(目前全部为DBR工艺),在前述芯片SEM图像中,焊盘正面平整面积较小,底层电极图像明显,因此在固晶过程中,芯片会产生轻微倾斜,后续回流焊过程中易在焊盘对应位置产生大量空洞,导致焊力不足;对于组3,由于后续镀锡制程所制作锡层厚度达10um,焊盘表面未表现出底层电极结构,相对平整,因此在固晶及过温后,芯片与基本贴合紧密,后期使用可靠性更高。

综合以上3组实验品情况,由于目前小尺寸芯片因可靠性问题都采用DBR结构的倒装结构,其底层一次电极结构在焊盘表面表现明显,且占据较大比例,因此电极表面采用AuSn结构(组2)在现有封装过程中易产生空洞,其并不适用于现有常规制程下的小尺寸倒装芯片。电极表面采用Au结构(组1),其采用锡膏方式固晶使用,能适用于现有制程,但使用过程中需结合焊盘大小选择合适粒径锡膏,有助于提高焊接可靠性,同时锡膏使用量对封装良率影响较大,电极表面采用镀Sn结构(组3),芯片制程较为复杂,对芯片良率稍有影响,但在封装过程及推力表现较优。

结论

基于前述实验及分析,针对目前微显示LED芯片焊盘结构,由于芯片工艺路线限制,AuSn结构不适用于该应用下芯片,表面Au结构,符合现有常规倒装芯片使用方式,但锡膏选择及封装过程控制要求较高,表面镀Sn结构,芯片制程较为复杂,成本略高,但封装使用效果较优,封装应用厂商可根据自己的需要选择合适芯片焊盘结构。

参考文献

[1]连程杰.LED芯片倒装技术简述[J].长江大学学报,(31):96-97[2]薛栋民.铝/镍/铜UBM厚度对SnAgCu焊点的力学性能及形貌影响[J].半导体光电..35(2):-[3]王阳元.集成电路工艺基础[M].北京:高等教育出版社,[4]程明生.倒装芯片热电极键合工艺研究[J].电子与封装..6(6):9-13

来源:华灿光电作者:张威,戴广超,付杰,陈亮,王江波

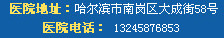

转载请注明地址:http://www.abmjc.com/zcmbwh/2166.html