上期话题

在追求PCBA板焊点牢靠的同时、也需要侧边pad有完美的上锡高度、确保焊接一版成功。大家觉得QFN有必要爬锡达到50%+以上吗?高于IPC三级标准?在今后的焊接过程中如何避免QFN侧边焊盘不上锡的问题?

(戳标题,即可查看上期文章回顾)

问

答

如何让QFN焊接爬锡高度达到50%以上

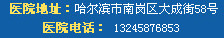

QFN(QuadFlatNo-leadPackage,方形扁平无引脚封装),表面贴装型封装之一,它通常是长方形或正方形,中间有一个大的接地焊盘,封装四侧配置有电极触点,由于无引脚,贴装占有面积比QFP小,高度比QFP低。由于QFN封装不像传统的SOIC与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电路径短,自感系数以及封装体内布线电阻很低,所以它能提供卓越的电性能。此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。通常将散热焊盘直接焊接在电路板上,并且PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。由于其本身没有引脚,封装周围的焊盘和PCB焊接实现电气连接,所以对焊接的工艺要求极高,特别是焊盘周围爬锡高度对于一些高靠性产品的稳定性有很大的影响,在文中根据我司平时生产中的一些实际案例和经验总结,列举了一系列的解决方案,得到了大家的积极响应,感谢大家的支持。

对于QFN侧边pad上锡高度达到50%以上的必要性,大家讨论和回复的是浓郁而热烈。个人建议这个标准可以执行,但是要根据产品的实际应用和需求来执行,一博科技做为拥有四家PCBA焊接工厂,PCB一站式服务的公司对大家的提出的独特见解和好的建议,要给一个大大的赞。比如网友龙凤呈祥的回复比较客观公正有说服力。

Itdepends….客户需求(客户是上帝)以及项目产品实际类型而定,不能一概而论:、若是军工级、航天级高精尖产品,肯定有必要爬锡达到50%以上,达到或高于IPC三级标准。若是一般产品就没必要了。一般的达到IPC二级标准就可以了,毕竟1.价格相对较低2.锡膏较多分布在QFN底下,机械强度较高。3.不涂助焊音也不会增加PCB二次腐蚀,采用一次性过炉,元件伤害相对较小。缺点是存在裸铜现象。、达到IPC三级标准以上,外观大于50%上锡,看起来较美观。但是1.价格相对较高2.将锡膏全部引到侧面上,底部锡膏会相对较少,反而会降低QFN的机械强度3.涂助焊膏需多次过回焊炉,对电子产品元件伤害较大,会加速元件老化和腐蚀等其他潜在问题。4.多次过回焊炉,增加来回动作,存在撞件等品质隐患。、实际中:使用活性较高的锡膏、钢网开孔略微涨价上锡量以及生产完用X-RAY检查是很常用的有效手段。

另外网友鹏的提问关于阻焊厚度的问题,不同产品要求是不同的,另外阻焊厚度高于焊盘,在开钢网时要注意优化钢网设计,防止焊接异常,大概总结如下:

(以下内容选自部分网友答题)

有必要。今后的焊接过程中,避免QFN侧边焊盘不上锡的问题,可以加点助焊剂,另外要保证焊锡量。

涌评分:2分

如果只考虑电性能我觉得没必要达到50%,但是考虑到可靠性比如附着力,阻焊等还是有必要的,毕竟达到50%的机械强度会好很多,外观也要好看些,同时锡膏包裹也可以防氧化

两处闲愁评分:2分

QFN的器件在BMS项目里对上锡要求就50%+,对于很多贴片厂有点难

大漠.樛木评分:2分

1.有必要达到IPC三级标准。2.是否高于标准依客户。3.用活性稍高的锡膏,钢网开孔在确保不连锡的情况增加锡量(厚度或者延伸引脚),检查印刷情况,元件贴装高度保持与锡膏接触层即可,元件生产前烘烤或要求供应商做氧化处理,生产完x-ray检查内部。

山水中石评分:3分

那针对A类和B类的这种贴片,在建封装的时候,对焊盘的尺寸要求能不能给出建议。

deam评分:2分

爬锡达到50%+以上,我觉得也不一定是都必须,有的民品产品没那么高要求是,应该不用达到这个高的标准。工艺复杂度高了,应该成本生产周期都会高啦。要避免QFN侧边焊盘不上锡,看来处处细节都不能忽视,锡膏、钢网开孔、焊盘表面处理等等

杆评分:3分

没有必要过设计,其他器件ipc2,就qfn是ipc3,甚至还要再高级。这只会增加成本,殊不知产品就是要上市快,成本低。改善qfn焊接:根据pdf推荐使用适当的钢网开口大小和钢网厚度,增加成本,增加焊接时氮气浓度,采用好的pcb表面处理工艺,绿油厚度严格控制,避免器件被“垫”高

欧阳评分:3分

要看所在的行业,所处的环境,国家的规定来确定是否要采用高于ipc3的焊接标准,一味的过设计,只会带来成本的浪费,不符合企业的利润最大化。想要改善qfn焊接:1,锡膏,pcb和qfn器件做好存储,密封等工作2,回流炉无氧焊接3,焊接后3daoi检查,Xray检查

Ben评分:3分

如何看积分排行榜:

在主页输入关键词:积分

高速先生精选★★★★★

回复数字获取往期文章。(向上滑阅览)

回复36→高速串行之S参数系列

回复35→高速串行之编码系列

回复34→高速串行之S参数-连接器系列

回复33→高速串行简史系列

回复32→电源系列(下)

回复31→电源系列(上)

回复30→DDR系列(下)

回复29→DDR系列(上)

回复28→层叠系列(下)

回复27→层叠系列(上)

回复26→拓扑和端接系列(下)

回复25→拓扑和端接系列(上)

回复24→反射详解系列文章

回复23→阻抗系列(下)

回复22→阻抗系列(中)

回复21→阻抗系列(上)

回复20→绕线与时序

回复19→SERDES与CDR系列

回复18→既等长,为何不等时系列

回复17→cadence等长处理规则设置

回复16→DDR时序学习笔记系列

回复15→串行系列

回复14→DDR信号完整性仿真介绍系列

回复13→PCB设计技巧分享一二

回复12→高速设计三座大山

回复11→PCB设计十大误区-绕不完的等长系列

回复10→PCB设计十大误区三

回复09→DDRX系列

回复08→高速串行系列

回复07→设计先生之回流设计系列

回复06→略谈AllegroPcbDesign小技巧

回复05→PCB设计十大误区一二

回复04→微带线系列

回复03→抽丝剥茧系列

回复02→串扰探秘系列

回复01→案例分享系列

转载请注明地址:http://www.abmjc.com/zcmbzl/2581.html