本文由半导体产业纵横综合整理自businesswire

“H-Cube”采用先进的硅中介层技术和混合基板结构,可实现6个HBM的高效集成,并具有更低的成本优势。

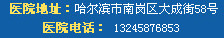

三星全新H-Cube封装解决方案的俯视图。(图片来源:美国商业资讯)

三星电子今天宣布,它已经开发出混合衬底立方体(H-Cube)技术,这是其最新的2.5D封装解决方案,专门用于高性能计算机、人工智能、数据中心、以及需要高性能和大面积封装技术的网络产品。

三星电子高级副总裁兼铸造市场战略团队负责人MoonsooKang表示,与三星电子机械(SEMCO)和Amkor技术联合开发的H-Cube解决方案适用于需要集成大量硅芯片的高性能半导体。“通过扩大和丰富代工生态系统,我们将提供各种一揽子解决方案,以在客户面临的挑战中找到突破。”

AmkorTechnology全球研发中心高级副总裁JinYoungKim表示,在当今对系统集成的要求越来越高且基板供应受限的环境中,三星代工厂和AmkorTechnology已成功共同开发H-Cube以克服这些挑战。“这一发展降低了进入HPC/AI市场的门槛,并展示了代工厂与外包半导体组装和测试(OSAT)公司之间的成功合作与伙伴关系。”

H-Cube结构与特征

2.5D封装使逻辑芯片或高带宽存储器(HBM)能够以较小的外形尺寸放置在硅插入器的顶部。三星的H-Cube技术采用混合基板、能够实现精细凹凸连接的细间距基板和高密度互连(HDI)基板,以实现2.5D封装的大尺寸。

随着高性能计算机、人工智能和网络应用市场所需规格的增加,安装在一个封装中的芯片数量和尺寸增加,加上对于高带宽通信的需要,大面积封装变得越来越重要。

当集成六个或更多HBM时,制造大面积衬底的难度迅速增加,导致效率降低。三星电子通过在高端微距基片下叠加易于大面积实现的HDI基片的混合基片结构,解决了这一问题。

将连接芯片和基板的焊锡球的间距比普通焊锡球的间距减少35%,可以将小间距基板的尺寸最小化,并在小间距基板下增加HDI基板(模块PCB),确保与系统板的连接。

此外,为了提高H-Cube解决方案的可靠性,三星应用了其专有的信号、电源完整性分析技术,该技术可以稳定供电,同时在堆叠多个逻辑芯片和HBM时将信号损失或失真降至最低。

展望未来,三星电子将于17日(PST)与生态系统合作伙伴共同举行“第三届三星先进代工生态系统(SAFETM)论坛”。

三星在2.5D封装领域的其他进展

今年5月,三星还发布了新一代2.5D封装技术I-Cube4集成四颗HBM。

并且宣布,新一代2.5D封装技术“I-Cube4”(InterposerCube4)已经正式投入商用,可用于HPC、AI、5G、云、数据中心等各种领域。

这是一种异构整合技术,可以在一个硅底中介层上,放置一颗或多颗逻辑芯片(CPU/GPU等),以及四颗HBM高带宽内存芯片,然后封装在一起,作为一颗芯片使用。

和当年AMDFiji系列显卡颇为相似,但显然不是简单复刻。

在以往的类似封装技术中,随着芯片复杂度的增加,硅底中介层也会越来越厚,三星I-Cube4则将硅底中介层控制在了区区微米左右,也就是仅仅0.1毫米,比一张纸还要薄,更方便在更大的面积上进行各种整合操作,提高产品质量。

另外,三星I-Cube4封装还有独特的架构和测试技术,可以有效提高散热效率、产品良率,进而节约成本。

三星在年推出了I-Cube2封装技术,年带来了X-Cube,今年3月搞定I-Cube4,目前还在开发更复杂的I-Cube6,可同时封装六颗HBM,以及更复杂的2.5D/3D混合封装技术。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。

转载请注明地址:http://www.abmjc.com/zcmbyf/5123.html